Bufferable writes with error may cause wrong mcause

Created by: silabs-oysteink

Bug Title

Bufferable writes with error may cause wrong mcause

Component

Component:RTL

Steps to Reproduce

There is currently no test case that shows this issue, but possible steps would be:

- A bufferable write is performed, and the data_rvalid + data_err comes late due to wait states.

- Any instruction with rf_we=1'b1 follows the load/store.

When the data_err arrives, ex_wb_pipe.rf_we may be either 0 or 1, causing the controller to latch the wrong cause for the NMI.

data_err is qualified in load_store_unit line 623:

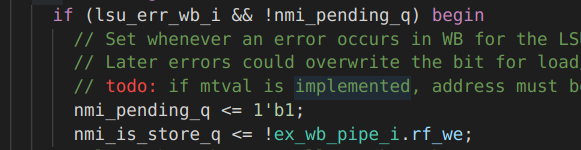

NMI is picked up in the controller, line 759:

An assertion should be made, that tracks OBI transfers and checks that an NMI is taken with the correct cause. This should fail with the current RTL. Once the assertion is in place, an RTL fix should be done. Possible fix can be to make the lsu_response_filter track the type of transaction related to every resp_valid, and directly output the error and type to the controller. Then the controller can disregard the ex_wb_pipe.rf_we and only look at the output from the response filter.