dcsr cause mismatch when entering debug after a step

Created by: strichmo

Component

Component:RTL

Steps to Reproduce

Please provide:

- Use the cv32e40x/dev branch of core-v-verif https://github.com/openhwgroup/core-v-verif.git

- Use this hash: 7d0b8501dafdd82ac02f997c70d7beed463be2b3

- Command line

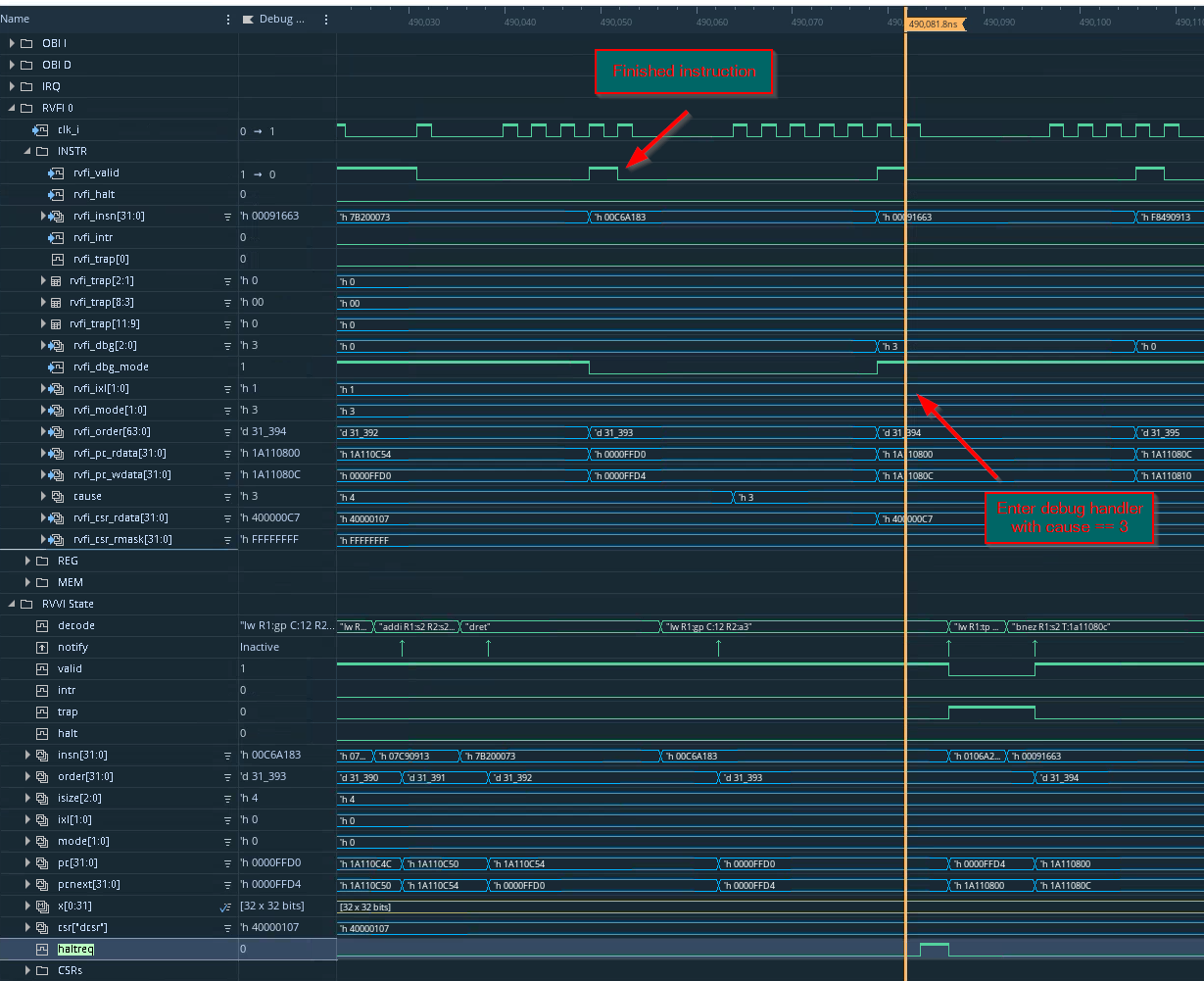

% makeuvmt comp_corev-dv gen_corev-dv test TEST=corev_rand_instr_obi_err_debug SEED=-1960056061 The core is in debug single-step mode and is single-stepping. The core exits debug mode with a dret and then executes a single instruction. When re-entering debug mode, there is also an external debug request. The core re-enters debug mode with a dcsr.cause of 3, which is external request. However the ISS believes that the cause should be 4, or step mode. Note that I am sending a pseudo-instruction with haltreq set before stepping into the debug handler, but the ISS leaves the dcsr.cause at 4 (step cause)

From the debug spec the debug_req has a higher priority to step in the dcsr.cause bitfield description. I would like for a member of the Cores team to look at this case before I file an issue on OVPSIM to get more clarification.