Wrong dcsr.cause after sleep

Created by: silabs-oysteink

Wrong dcsr.cause after sleep

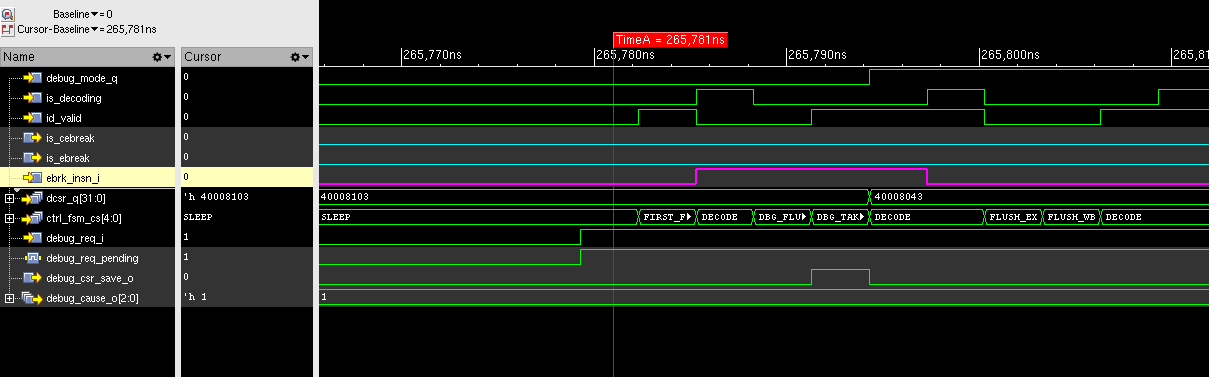

Cause bits in dcsr seems to wrong if the first instruction decoded after WFI + debug_req_i is an EBREAK.

- Core is sleeping

- debug_req_i is asserted

- Core wakes up, fetches an ebreak instruction

- Core enters debug mode, sets cause to 0x1 (ebreak)

- Ebreak instruction does not retire

Debug spec v 0.13.2 states the following:

If halt is requested while wfi is executing, then the hart must leave the stalled state, completing this instruction’s execution, and then enter Debug Mode.

In this case, I would expect the core to disregard the ebreak and enter debug mode with cause=0x3 (external debugger). Instead it enters debug as if the ebreak caused it, although the ebreak does not retire.

Component

Component:RTL

Steps to Reproduce

- Clone my fork of core-v-verif: https://github.com/silabs-oysteink/core-v-verif.git

- Check out branch silabs-oysteink_random-debug

- from cv32/sim/uvmt_cv32: 4: make comp_corev-dv gen_corev-dv TEST=corev_rand_debug START_INDEX=0 NUM_TESTS=1 5: make test TEST=corev_rand_debug RUN_INDEX=0 WAVES=YES USE_ISS=NO

I've disabled the ISS as the current state of the repo requires an invalid license. Assertion will fire regardlessly.