interrupt CSR checks fail when interrupt occurs during div instruction

Created by: strichmo

When enabling random interrupts with the ISS in the core-v-verif testbench CSR miscompares can occur on instruction retirement boundaries.

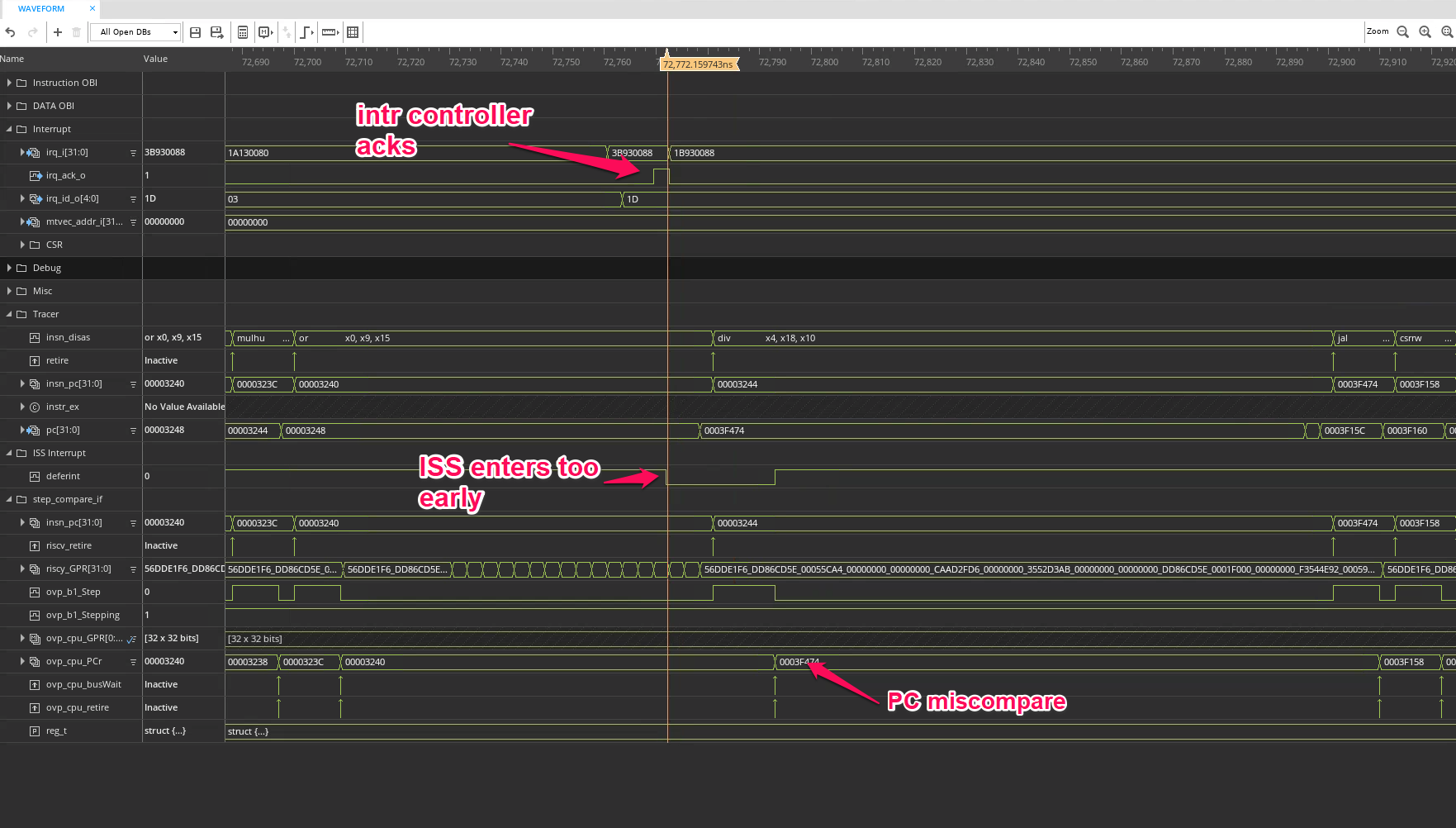

The testcase is an interrupt that is acknowledge during a div instruction. See the first figure below.

In this case the interrupt is acknowledge 2 instruction retirements before the machine mode interrupt vector is entered. Therefore the PC is miscompared against the ISS.

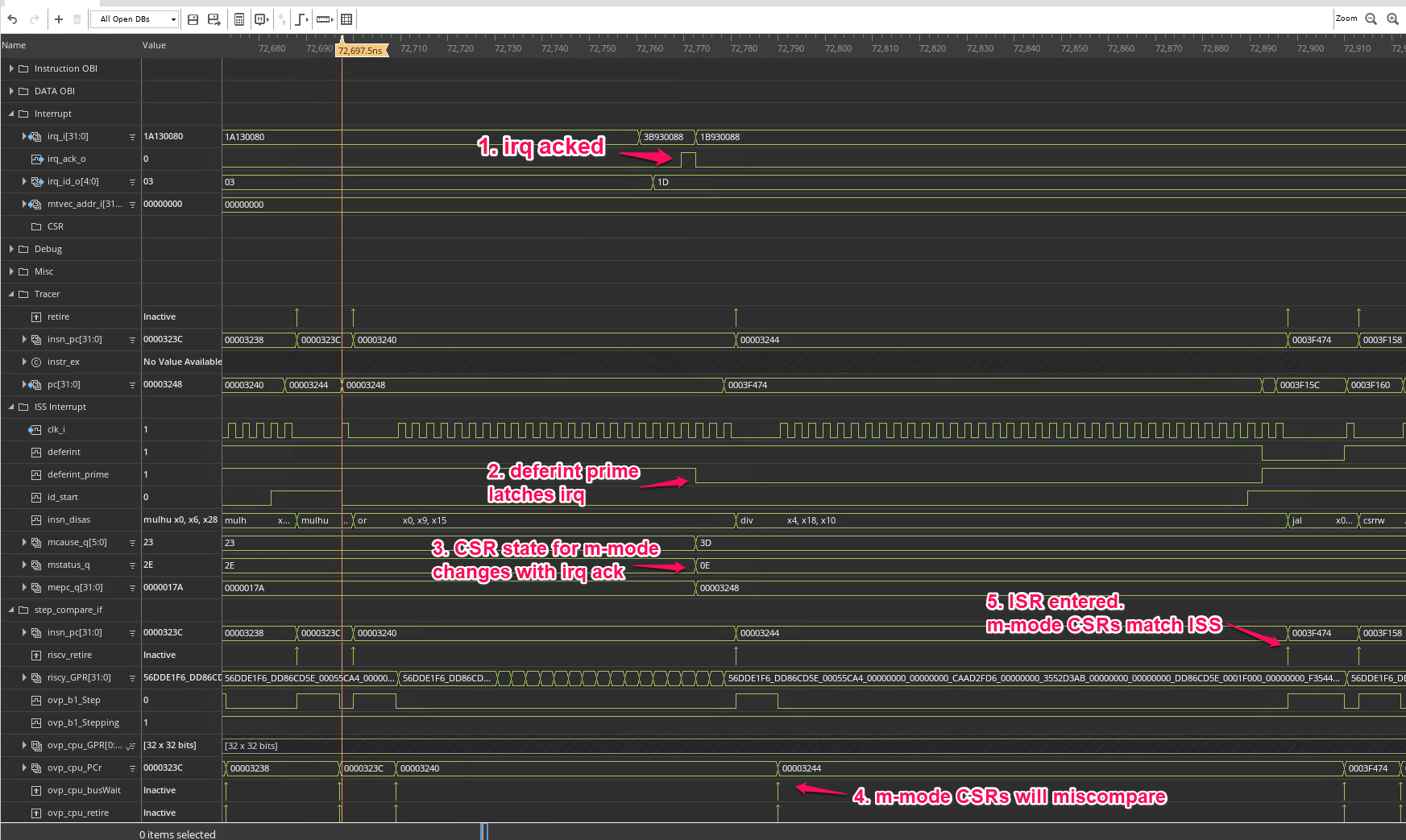

To address this I added a staging of the "deferint" signal which masks the irq assertion in the ISS to the second instruction. This enables the PCs to compare properly between RTL and the ISS.

However with this case, the CSRs for machine mode interrupts (mepc, mstatus, mcause) will miscompare on the first instruction retirement because the RTL updates the CSRs immediately upon interrupt acknowledgement.

Steps to Reproduce

To replicate the first condition (PC miscompare):

-

Use this branch and fork: https://github.com/strichmo/core-v-verif/tree/strichmo/irq_random_fail_0

-

Run this in cv32/sim/uvmt_cv32 % make corev-dv gen_corev_rand_interrupt_test NUM_TESTS=1 SEED=1 % make custom CUSTOM_PROG=corev_rand_interrupt_test_0 USER_RUN_FLAGS="+gen_irq_noise +UVM_MAX_QUIT_COUNT=20,NO" SIMULATOR=xrun

To replicate with the proposed "deferint_prime" fixes:

-

Use this branch and fork: https://github.com/strichmo/core-v-verif/tree/strichmo/irq_random_fail_fix_0

-

Run the same tests: % make corev-dv gen_corev_rand_interrupt_test NUM_TESTS=1 SEED=1 % make custom CUSTOM_PROG=corev_rand_interrupt_test_0 USER_RUN_FLAGS="+gen_irq_noise +UVM_MAX_QUIT_COUNT=20,NO" SIMULATOR=xrun

UVM_ERROR @ 72790.000 ns : uvmt_cv32_step_compare.sv(79) reporter [Step-and-Compare] mcause expected=0x80000003 and actual=0x8000001d PC=0x00003244 UVM_ERROR @ 72790.000 ns : uvmt_cv32_step_compare.sv(79) reporter [Step-and-Compare] mepc expected=0x0000017a and actual=0x00003248 PC=0x00003244 UVM_ERROR @ 72790.000 ns : uvmt_cv32_step_compare.sv(79) reporter [Step-and-Compare] mstatus expected=0x00001888 and actual=0x00001880 PC=0x00003244