Data address is not consistent with byte enable signals

Created by: Silabs-ArjanB

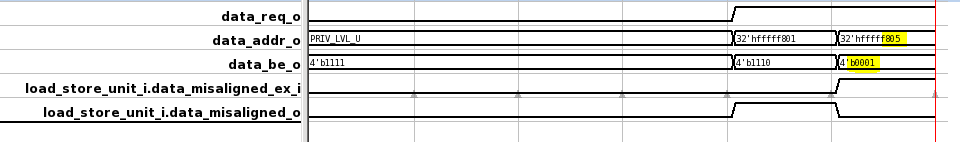

In the second phase of a non-aligned load/store the data address (data_addr_o) is not consistent with the byte enables (data_be_o).

For example when doing a word write to address 0xffff_f801 we will get two transfers:

- First transfer of 3 bytes: Address 0xffff_f801, byte lanes 4'b1110

- Second transfer of 1 byte: Address 0xffff_f805, byte lanes 4'b0001

Slaves can of course simply ignore the 2 LSBs of the address. The OBI spec however requires the address to be consistent with the byte lanes (which will enable an easier translation to AXI). As the second transfer will always have its LSB set (data_be_o[0] is always 1), the 2 LSBs of the address must always be 0 for that second transfer.

The fix is easy (and I already did it on the pull request that I soon plan to issue):

Replace the following line in riscv_load_store_unit-sv:

assign data_addr_o = data_addr_int;

with:

assign data_addr_o = data_misaligned_ex_i ? {data_addr_int[31:2], 2'b00} : data_addr_int;