Problem on second requisition on misaligned stores

Created by: aignacio

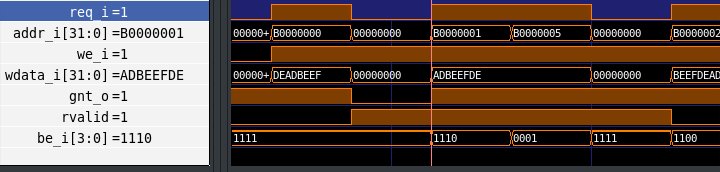

Hi everyone, I have been designing a dbus to ahb converter for RI5CY cpu and I have a question related to set the converter to operate with two-cycle misaligned requisitions. So, considering that a memory or cache interface could handle misaligned requisitions through ahb bus, how did you make the conversion in terms of AHB Address considering the two LSBs from the req/grant interface? I mean, as an example here below, have a word to store shifted by one byte into (0xb000_0000), so the first req. makes sense ahb addr == addr_i but in the second requisition to store the remaining byte, the addr_i it's equal to 'h5, what indeed would shift the data by one byte once you make ahb_addr == addr_i, IMO the addr should be 'h4 (nxt word boundary), isn't it?

li t0, 0xDEADBEEF

li t1, 0xB0000000

nop

sw t0, 0(t1) # 0xB0000000 = DEADBEEF / 0xB0000004 = 00000000

nop

sw t0, 1(t1) # 0xB0000000 = ADBEEFEF / 0xB0000004 = 000000DE