issue with DPC register behavior (same is with MEPC)

Created by: Itaykeidar

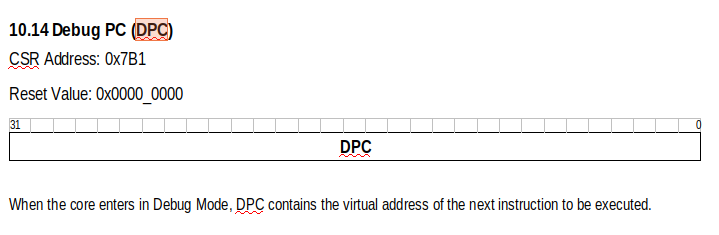

Here is definition of this register from the specification:

Test executed following instruction: csrrsi a6, dpc, 27 27 in this print is decimal value. As the result of instruction execution register a6 will contain old value of dpc register and dpc register will be updated by next formula: dpc = dpc | 27. Old value of dpc register is 0xa. Following upper formula new value should be dpc = 0xa | 0x1b = 1b.

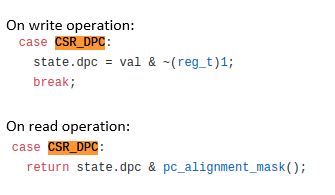

In this case spike calculated it differently. DPC register in the spike is 0x1a. I tried to debug this issue and I found that spike performs some alignment of dpc register value.

Path to source code on github: https://github.com/riscv/riscv-isa-sim/blob/master/riscv/processor.cc

Can you please advise if this is a bug / spec clarification, or do we need for such address alignments of dpc register on spike side

as stated in title, this is in mepc reg same behavior.