ISS: Mismatch on GPRs when clearing/setting dcsr bits in debug mode

Created by: silabs-hfegran

DCSR read/write bitfields GPR read value mismatch in debug mode

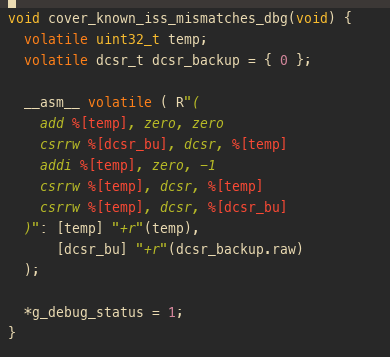

The following sequence of operations creates ISS mismatches, where the reference model appears to readback the value it wrote, not the value that was present prior to the csrrw instruction: enter debug mode, read dcsr and write all 0s, read dcsr and write all 1s, read dcsr and write back original value.

Type

- Functionally incorrect behavior

Steps to Reproduce

Please provide:

- cv32e40s/dev 04a877e9

- make test TEST=debug_test2 CFG=default USE_ISS=1 (This is at the end of a larger test, to only run this failing part, change the START_TEST_NUM define in debug_test2.c to 18)

Info (IDV) Instruction executed prior to mismatch '0x3230(cover_known_iss_mismatches_dbg+12): 7b0717f3 csrrw x15,dcsr,x14'

Error (IDV) GPR register value mismatch (HartId:0, PC:0x00003230 cover_known_iss_mismatches_dbg+12):

Info (IDV) 0> GPR x15

Info (IDV) . dut:0x400004d3

Info (IDV) . ref:0x400000d0

UVM_ERROR @ 40542.300 ns : rvvi-pkg.sv(93) reporter [] uvmt_cv32e40s_tb.imperas_dv.idv_trace2api.state_compare @ 40542.000 ns: MISMATCH

Info (IDV) Instruction executed prior to mismatch '0x3234(cover_known_iss_mismatches_dbg+16): 577d c.li x14,-1'

Error (IDV) GPR register value mismatch (HartId:0, PC:0x00003234 cover_known_iss_mismatches_dbg+16):

Info (IDV) 1> GPR x15

Info (IDV) . dut:0x400004d3

Info (IDV) . ref:0x400000d0

UVM_ERROR @ 40551.300 ns : rvvi-pkg.sv(93) reporter [] uvmt_cv32e40s_tb.imperas_dv.idv_trace2api.state_compare @ 40551.000 ns: MISMATCH

Info (IDV) Instruction executed prior to mismatch '0x3236(cover_known_iss_mismatches_dbg+18): 7b071773 csrrw x14,dcsr,x14'

Error (IDV) GPR register value mismatch (HartId:0, PC:0x00003236 cover_known_iss_mismatches_dbg+18):

Info (IDV) 2> GPR x14

Info (IDV) . dut:0x400000d0

Info (IDV) . ref:0x40009cd7

Info (IDV) 3> GPR x15

Info (IDV) . dut:0x400004d3

Info (IDV) . ref:0x400000d0

UVM_ERROR @ 40557.300 ns : rvvi-pkg.sv(93) reporter [] uvmt_cv32e40s_tb.imperas_dv.idv_trace2api.state_compare @ 40557.000 ns: MISMATCH

Info (IDV) Instruction executed prior to mismatch '0x323a(cover_known_iss_mismatches_dbg+22): 7b079773 csrrw x14,dcsr,x15'

Error (IDV) GPR register value mismatch (HartId:0, PC:0x0000323a cover_known_iss_mismatches_dbg+22):

Info (IDV) 4> GPR x14

Info (IDV) . dut:0x40009cd7

Info (IDV) . ref:0x400000d0

Info (IDV) 5> GPR x15

Info (IDV) . dut:0x400004d3

Info (IDV) . ref:0x400000d0

UVM_ERROR @ 40566.300 ns : rvvi-pkg.sv(93) reporter [] uvmt_cv32e40s_tb.imperas_dv.idv_trace2api.state_compare @ 40566.000 ns: MISMATCH

Info (IDV) Instruction executed prior to mismatch '0x323e(cover_known_iss_mismatches_dbg+26): c43a c.swsp x14,8(x2)'

Error (IDV) GPR register value mismatch (HartId:0, PC:0x0000323e cover_known_iss_mismatches_dbg+26):

Info (IDV) 6> GPR x14

Info (IDV) . dut:0x40009cd7

Info (IDV) . ref:0x400000d0

Info (IDV) 7> GPR x15

Info (IDV) . dut:0x400004d3

Info (IDV) . ref:0x400000d0

UVM_ERROR @ 40575.300 ns : rvvi-pkg.sv(93) reporter [] uvmt_cv32e40s_tb.imperas_dv.idv_trace2api.state_compare @ 40575.000 ns: MISMATCH